## Continuous Assessment Test I - January 2025

| Programme | : B.Tech (ECE)                                                  | Semester   | :  W | S 2024-25                                          |

|-----------|-----------------------------------------------------------------|------------|------|----------------------------------------------------|

| Course    | :                                                               | Code       | : BE | ECE303L                                            |

|           | VLSI System Design                                              | Class Nbr  | CH   | H2024250502913<br>H2024250502914<br>H2024250503037 |

| Faculty   | : Dr. A. Ravi Sankar, Dr.S.Umadevi,<br>Dr. Pritam Bhattacharjee | Slot       | : E1 | +TE1                                               |

| Time      | : 90 Minutes                                                    | Max. Marks | : 50 |                                                    |

## General Instructions:

Write only your registration number on the question paper in the box provided and do not write other information

## Answer ALL the questions

|   | Q.No.            | Sub.<br>Sec. | Questions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             | BT<br>LEVEL |

|---|------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|

|   | ×                | 2            | <ul> <li>i. With the neat sketch discuss about semicustom VLSI design flow.</li> <li>ii. Elucidate Moore's Law and classify the different integrated circuit (IC) technologies based on their transistor count.</li> </ul>                                                                                                                                                                                                                                                                                                                        | 10<br>[7+3] | L1          |

|   | B <sup>2</sup> / | ~            | Derive the expression for the drain current of an N-channel enhancement-type MOSFET from first principles, also indicate the change in the drain current expression due to velocity saturation and channel length modulation.                                                                                                                                                                                                                                                                                                                     |             |             |

| 4 |                  |              | Consider the nMOS transistor which has W/L= 2. In this process, the gate oxide thickness is 12Å. The mobility of electrons is $80 \text{cm}^2/\text{V} \cdot \text{s}$ . The threshold voltage is 0.3V. Plot $I_{ds}$ vs. $V_{ds}$ for the following cases.  i. $V_{gs} = 0.5 \text{V}$ with $V_{ds} = 0.1 \text{V}$ and $V_{ds} = 0.6 \text{V}$ ii. $V_{gs} = 0.8 \text{V}$ with $V_{ds} = 0.1 \text{V}$ and $V_{ds} = 0.6 \text{V}$ (Given: $\epsilon_{oxide} = 3.9 \times \epsilon_0$ where $\epsilon_0 = 8.85 \times 10^{-14} \text{F/cm}$ .) |             | 1.4         |

|   | Ð                |              | Plot the Voltage Transfer Characteristics (VTC) of a static CMOS inverter and clearly indicate the various regions along with the operating conditions of both the pMOS and nMOS transistors. Provide the expressions for the input and output transition points corresponding to the various operating regions of the inverter.                                                                                                                                                                                                                  |             | 1.3         |

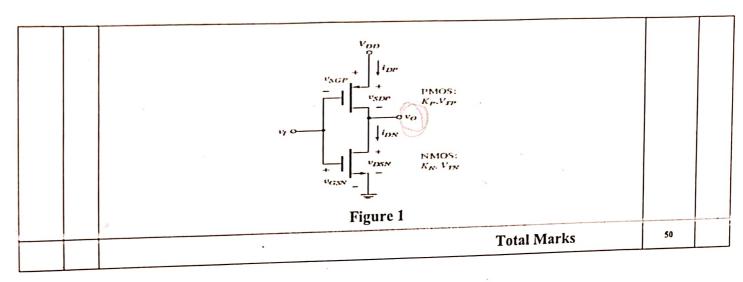

|   | <b>s</b> .       |              | Consider the CMOS inverter shown in Figure 1. Assume $V_{DD}=2~V~V_{thn}=\left V_{thp}\right =0.5~V,~\left(\frac{W}{L}\right)_n=\frac{2~\mu m}{1~\mu m}~,~\left(\frac{W}{L}\right)_p=\frac{2~\mu m}{1~\mu m}~,~\mu_nC_{ox}=200~\frac{\mu A}{V^2}~,\mu_pC_{ox}=100~\frac{\mu A}{V^2},\lambda_{n,p}=0,$ i. Find the input transition voltage  ii. Find the output voltage for (i) $V_i=0.6~V$ (ii) $V_i=1.2~V$                                                                                                                                      | 10<br>[2+8] | ы           |

Course Faculty